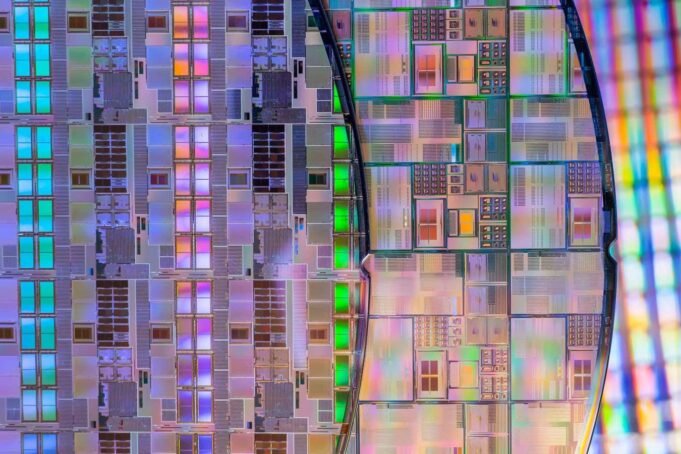

Gli attuali chip di silicio sono estremamente densi, ma i materiali 2D ultrasottili potrebbero renderli ancora più compatti

Wu Kailiang/ Alamy

Chip di memoria di lavoro spessi solo 10 atomi potrebbero portare a capacità di archiviazione radicalmente più grandi in dispositivi elettronici come gli smartphone.

Dopo decenni di miniaturizzazione, gli attuali chip dei computer contengono ora componenti incredibilmente piccoli, che spesso racchiudono decine di miliardi di transistor in un’area grande quanto un’unghia. Ma mentre le dimensioni dei componenti sui wafer di silicio sono diventate estremamente ridotte, i wafer stessi rimangono relativamente spessi, il che significa che ci sono limiti a quanto è possibile aumentare la complessità dei chip posizionando più strati uno sopra l’altro.

Gli scienziati stanno lavorando su chip più sottili realizzati con i cosiddetti materiali 2D come il grafene, che è costituito da un singolo strato di atomi di carbonio ed è teoricamente sottile quanto qualsiasi altro materiale. Ma fino ad ora con tali materiali era possibile realizzare solo chip semplici ed era difficile collegarli ai processori convenzionali e integrarli nei dispositivi elettrici.

Ora Chunsen Liu Lui e i suoi colleghi dell’Università Fudan di Shanghai hanno combinato un chip 2D spesso circa 10 atomi con un tipo di chip chiamato CMOS, attualmente utilizzato nei computer. Il modo in cui vengono prodotti questi chip risulta in una superficie ruvida, rendendo difficile la posa di un foglio 2D su di essa. Liu e i suoi colleghi hanno superato questo problema separando il chip 2D da un chip CMOS convenzionale con uno strato di vetro, che non fa parte dei processi attuali e richiederebbe l’industrializzazione prima della produzione di massa.

Il prototipo del modulo di memoria di lavoro del team ha raggiunto una precisione superiore al 93% nei test. Anche se questo è ben al di sotto dell’affidabilità richiesta per i dispositivi di consumo, rappresenta una promettente prova di concetto.

“Si tratta di una tecnologia molto interessante con un enorme potenziale, ma ha ancora molta strada da fare prima che diventi commercialmente fattibile”, afferma Steve Farber All’Università di Manchester, nel Regno Unito.

Kai Ju Il King’s College di Londra afferma che ridurre ulteriormente la progettazione dei chip attuali senza utilizzare materiali 2D sarebbe problematico perché si verifica una perdita di segnale quando i componenti convenzionali sono realizzati con larghezze estremamente ridotte. Questo effetto può essere superato riducendo lo spessore degli strati, il che significa che la miniaturizzazione in termini di spessore può potenzialmente consentire un’ulteriore miniaturizzazione in larghezza.

“Il silicio ha già superato queste barriere”, afferma Xu. “I materiali 2D potrebbero essere in grado di superare questi effetti. Se è molto sottile, il controllo sul cancello può essere più uniforme, più perfetto, quindi ci sono meno perdite.”

Soggetto: